为了提升我国处理器设计和应用水平,降低国产处理器设计门槛,培养高端设计人才,满足中小型设计企业和系统企业面向新兴应用市场对自主可控处理器的需求,厦门市海沧区科技局、凯发K8一触即发清华大学微电子学研究所、厦门半导体投资集团有限公司共同建立了“开源嵌入式处理器暨SoC设计技术服务平台”。项目落地厦门海沧,第一期为期三年,以基于RISC-V指令集,研发与ARM Cortex-A7性能相当的单核、多核处理器内核IP并集成AI人工智能硬件加速器为研发目标。目前,项目已进入第二年实施,各项工作稳步推进,并在40nm工艺上进行了第一次流片验证。流片处理器内核经实测,Dhrystone 跑分1.81,Coremark 跑分2.88,与ARM Cortex-A7内核基本相当。

项目组成员均为清华大学微电子所硕士毕业生,具有多年的处理器芯片设计和验证经验。团队成员参与研发的密码处理器IP曾获得北京市2018年度科学技术一等奖。凯发K8一触即发本次基于RISC-V指令集的Egret处理器设计,将多年的技术积累充分应用,并不断发展壮大。

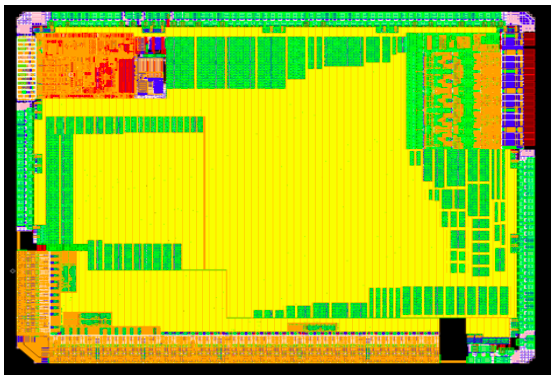

Egret处理器由厦门半导体投资集团有限公司和清华大合开发,是一款面向嵌入式系统的高性能处理器。基于RISC-V RV32IMAFC指令集进行自主设计,能够确保CPU的各个环节自主可控。内核采用九级流水线架构,顺序双发射,动态分支预测技术以及低功耗设计方法,内部集成了内存管理单元,物理内存保护单元以及指令和数据缓存单元,实现了对中断、调试、片外存储及外设的有效支持。可根据具体的应用需求进行特定的优化,扩展指令功能,满足客户定制化的需求。

Egret处理器可广泛应用于移动终端类设备,充分满足关键部件国产化的需求,为移动终端类产品提供坚实的性能保障。

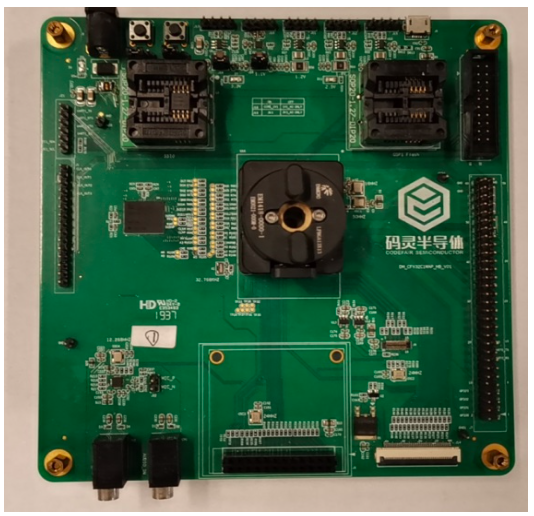

Egret处理器采用SIMC 40nm LL工艺进行流片,经过样片实测,频率可达到600MHz,Dhrystone性能1.81 DMIPS/MHz,Coremark性能2.88 Coremark/MHz,支持定时器中断、软件中断以及最多64个外部中断,支持单精度浮点运算,包含32KB D-Cache和32KB I-Cache。Egret处理器兼容AXI4接口,实现对SoC中的ARM Cortex-A7原位替换,可为企业节约大量的直接、间接研发经费,也能避免由于外部因素引发的指令集架构授权风险。

国芯科技新一代汽车电子高端MCU芯片获得批量订单,与易鼎丰携手打造VCU领域更具竞争力的解决方案

手机:15817255623

手机:15817255623  邮箱:admin@zghxzs.com

邮箱:admin@zghxzs.com  传真:+15817255623

传真:+15817255623  地址:江苏省常州市新北区创业路16号粤海工业园3C

地址:江苏省常州市新北区创业路16号粤海工业园3C